|

| [사진출처=연합뉴스] |

이 소식통은 TSMC가 AI 산업의 폭발적인 성장에 따라 애플과 엔비디아, 퀄컴, AMD 등 고객사의 수요가 증가하는 것에 비해 3나노 생산시설 확충에 나섰다면서 이같이 밝혔다.

이어 TSMC의 3나노 생산시설의 설비 확충과 100% 가동 등에 힘입어 올해 말까지 3나노 공정 월 생산량이 전년대비 30% 이상 증가한 12만개 이상이 될 것이라고 설명했다.

그러면서 지난해 4분기 TSMC 매출의 26%에 불과했던 3나노 공정이 ‘칩 온 웨이퍼 온 서브스트레이트’(CoWoS) 패키징과 함께 올해 TSMC의 성장 모멘텀이 될 것이라고 강조했다.

다른 소식통은 12인치(305㎜) 3나노와 5나노 웨이퍼를 생산하는 남부과학단지 내 TSMC 18팹(fab·반도체 생산공장)의 5나노 공정의 월 생산능력이 약 15만개에 달한다고 밝혔다.

이어 TSMC가 대형 고객사의 수요에 대처하기 위해 향후 5나노 생산시설을 확충하지 않고 3나노 생산시설을 늘릴 예정이라고 설명했다.

그러면서 TSMC의 이런 행보가 AI 칩 선두 주자 엔비디아의 그래픽처리장치(GPU) 블랙웰 후속 칩인 루빈의 3나노 공정 채택 가능성과 관련이 있는 것으로 풀이했다.

나노는 반도체 회로 선폭을 의미하는 단위로 선폭이 좁을수록 소비전력이 줄고 처리 속도가 빨라진다. 현재 세계에서 가장 앞선 양산 기술은 3나노다.

TSMC는 2나노 이상 최첨단 부문에서 대체로 우세한 것으로 전문가들은 평가하고 있다.

[ⓒ 매일경제 & mk.co.kr, 무단전재 및 재배포 금지]

화제의 뉴스

오늘의 이슈픽

인기 영상

가장 많이 본 뉴스

- 1미·중 통상협상 개시…관세전쟁 해빙 전환점 될까

- 2경제 격변기 재테크 전략은?…'2025 서울머니쇼'...

- 3"재생의료 게임체인저"…오가노이드사이언스, 오늘 코...

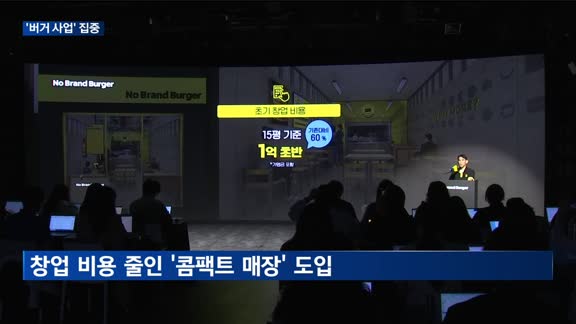

- 4외식 사업 재정비 나선 '신세계푸드'…'노브랜드 버...

- 5오가노이드사이언스, 코스닥 입성…상장 첫날 강세

- 6사모펀드 케이엘앤파트너스, 1천900억원에 마녀공장...

- 7이더리움 15% 폭등…가상화폐 시장 훈풍에 독주

- 8매일경제TV증시 오늘 ‘핫이슈’ “4년 괴로움의 끝...

- 9트럼프, 미·영 무역합의 발표 임박…"첫 번째 국가...

- 10[매일경제TV 야간투자본부] "수익률의 승부사"…M...

투데이 포커스

화제의 뉴스

포토뉴스

![[집중취재] 어두운 국내 경제 전망…발등에 불 떨어진 '경기 부양'](https://imgmm.mbn.co.kr/vod/news/103/2025/05/09/20250509164840_10_103_0_MM1005549295_4_259.jpg)

![[밸류업5000] 밸류업 시행 1년…자사주 취득액 연간 20조원 '첫 돌파'](https://imgmm.mbn.co.kr/vod/news/103/2025/05/09/20250509164840_10_103_0_MM1005549153_4_98.jpg)

![[밸류업 5000] 삼성전자, 밸류업 지수서 빠지나…공시 자료 미제출](https://imgmm.mbn.co.kr/vod/news/103/2025/05/09/20250509162952_10_103_0_MM1005549161_4_20.jpg)

![[밸류업 5000] 코웨이, 1천100억 자사주 매입 결정](https://imgmm.mbn.co.kr/vod/news/103/2025/05/09/20250509162952_10_103_0_MM1005549160_4_21.jpg)